# Open-access silicon photonics technologies of ePIXfab members: updates 2021

### Dr. Abdul Rahim

Disclaimer: The technology update information is provided by the respective foundries.

ePIXfab - the European Silicon Photonics Alliance

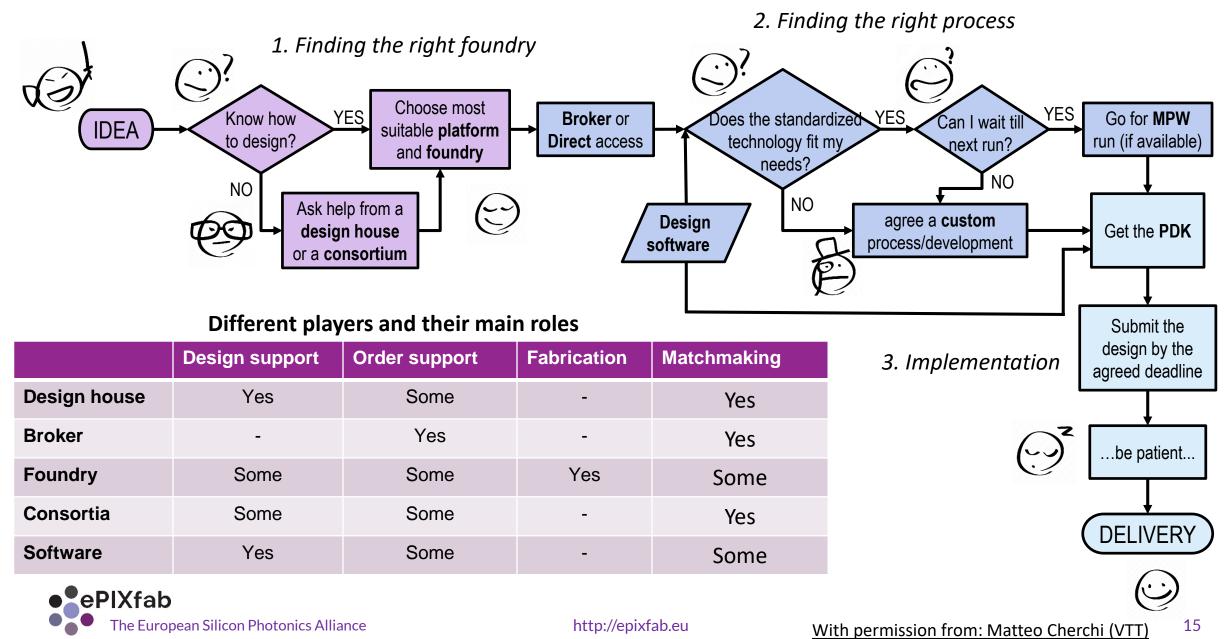

# How do you select the right foundry?

Important questions to ask yourself (or a design house/consortium):

- Which is the best platform for my application?

- What volumes do I require?

- Is the MPW offering suitable for my application?

- Does the MPW timetable suit my schedule?

- What are the prospects for scaling up volumes?

- What are the IP terms?

- What is the most cost effective fabrication technology for my application?

- Are the standard building blocks suitable for my design?

- What level of design support do I require?

http://epixfab.eu

With permission from: Callum Littlejohns (Cornerstone)

## How do you select the right foundry?

### Example: High speed transceiver prototype:

1. What is the best platform for my application?

2. Which foundry offers the required functionality? High speed modulator and photodetector

SUNY POLYTECHNIC CompoundTer

amf MICRO FOUNDRY

amf HOVANCED

FOUNDRIES

FOUNDRIES

TOWERIC

leti

Ceatech

umec 🤜

**APPLIED NANOTOOLS**

3. Which foundry is the most cost effective for low volumes?

National

SUNY POLYTECTINIC

**MPW** capability

**Thin SOI**

http://epixfab.eu

leti

latech

CompoundTer

FOUNDRIES

With permission from: Callum Littlejohns (Cornerstone)

## How can you benefit from the open-access community?

1. High risk device level innovation using e-beam lithography (early stage research)

2. Transfer device fabrication to DUV processes using flexible platforms (prototyping)

3. Dedicated engineering batch/s at low/medium volume foundry (manufacturing)

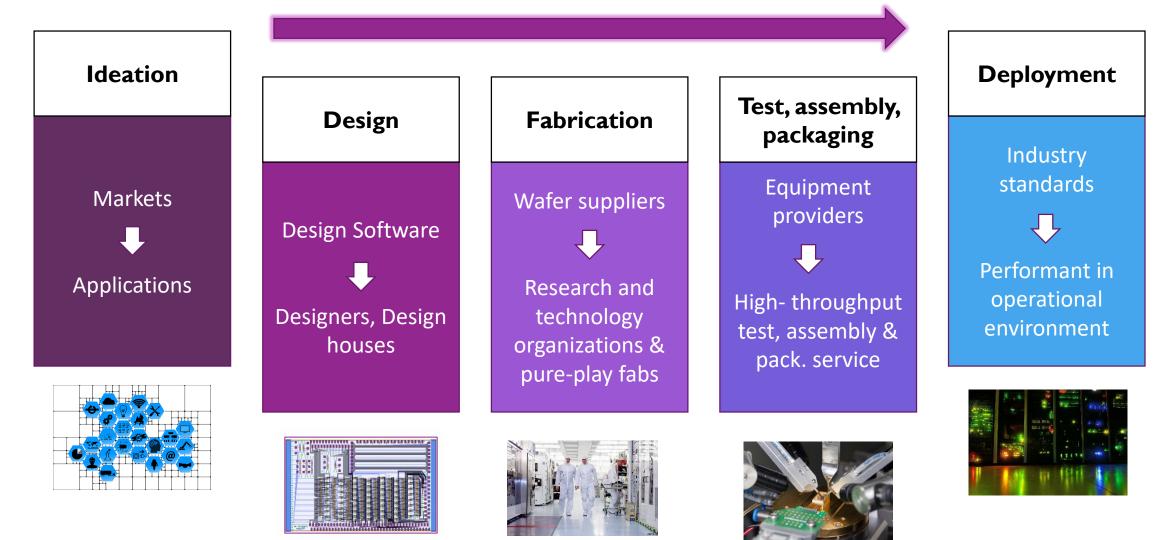

### **Silicon Photonics Ecosystem: Ideation to Deployment**

### Silicon Photonics Design

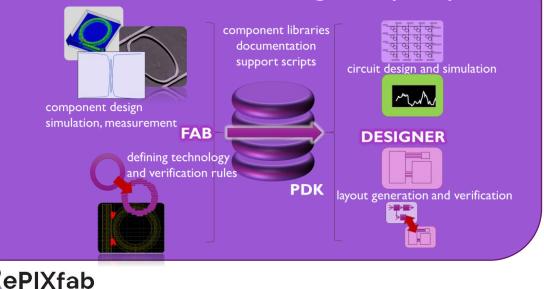

### **Status of Silicon Photonics Design Flow**

- Physical-level design and simulation

- Circuit-level design and simulation

- System-level simulation

- Design layout and verification

- Schematic-driven layout

- Layout-vs-Schematic verification

- Co-integration of electronic and photonic designs

BRIGHT LUCEDA Optiwave Photon Syndrys Syndrys Avenue

- Yield prediction and variability analysis

#### The Role of Process Design Kit (PDK)

#### **Current status of Silicon Photonics PDKs**

| Attribute            | Definition                                   | Electronics | Photonics |

|----------------------|----------------------------------------------|-------------|-----------|

| Tech.<br>Data        | Details about technology & processes         |             |           |

| Device<br>library    | Collection of tested building blocks         |             |           |

| P-cells              | Parametric cells of the building blocks      |             |           |

| DRC                  | Design rule contraints                       |             |           |

| Simulation<br>Models | Compact models of the building blocks        |             |           |

| Corner<br>Models     | Impact of extremity of fabrication parameter |             |           |

| Stochastic<br>Models | Impact of stochastic fabrication tolerances  |             |           |

| Reliablity           | Reliablity data of building blocks           |             |           |

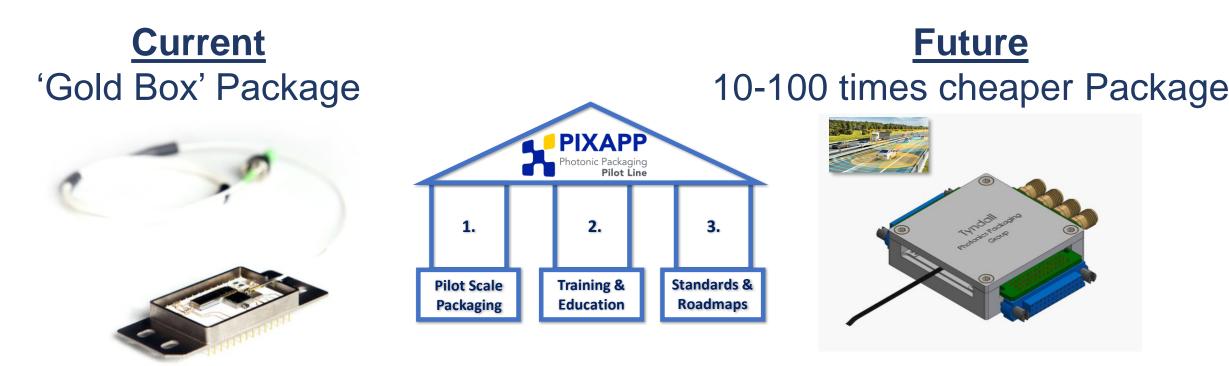

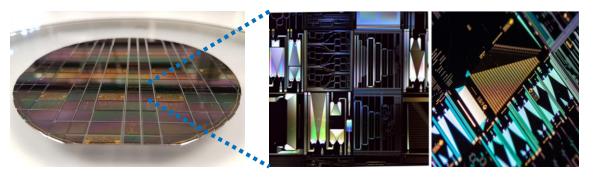

## **The Future of Photonic Packaging**

component-level packaging *High Throughput wafer-level packaging*

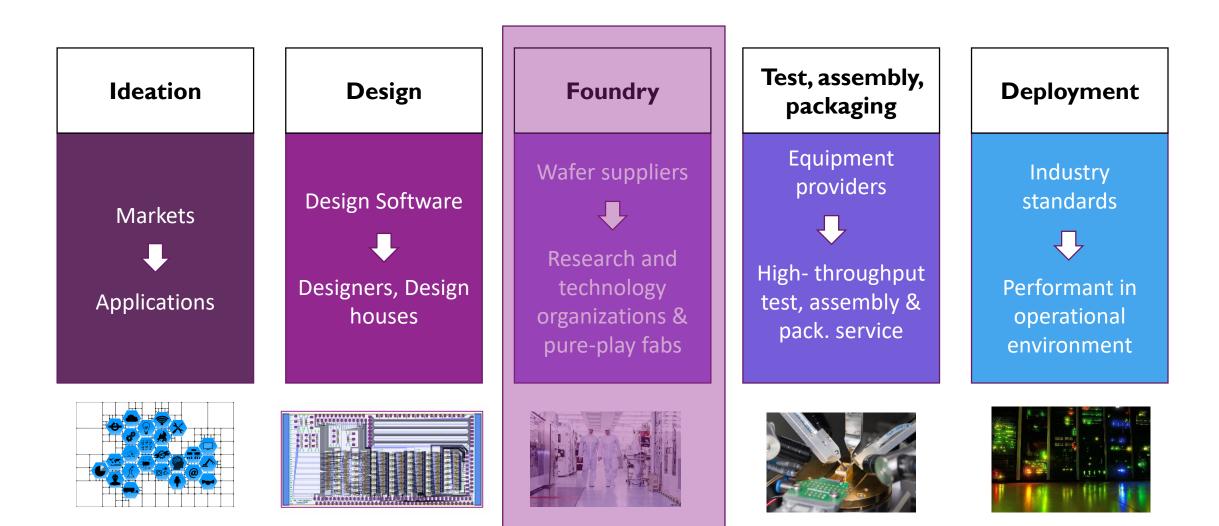

### **Silicon Photonics: Ideation to deployment**

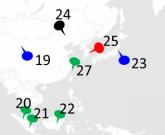

### Who fabricates silicon photonics ICs?

#### NOERH AMERICA

- 1. ULL Technologies (USA)

- 2. Applied Nanotools Inc. (Canada)

- 3.Intel (USA)

- 4. Tower Semicon. (USA)

- 5. Globalfoundries (USA)

- 6.AIM Photonics (USA)

•2

**2**3 4

#### ASIA

19. CUMEC (China)

20. Advanced Micro Foundry (Singapore)

21. CompoundTek (Singapore)

22. SilTerra (Malaysia)

23. PETRA (Japan)

24. IMECAS (China)

25. SAMSUNG (Korea)

26. Australian Silicon Photonics (Australia)

27. TSMC (Taiwan)

| EUROPE                     |                                   |  |

|----------------------------|-----------------------------------|--|

| 7. VTT (Finland)           | 13. LETI (France)                 |  |

| 8. SiPhotonic (Denmark)    | 14. CNM-IMB (Spain)               |  |

| 9. Imec (Belgium)          | 15. LioniX Int. (the Netherlands) |  |

| 10. Cornerstone (UK)       | 16. STMicro. (France)             |  |

| 11. IHP (Germany)          | 17. AMO GmbH (Germany)            |  |

| 12. LIGENTEC (Switzerland) | 18. CNIT (Italy)                  |  |

|                            | 28. STMicro (France)              |  |

| Alliance                   | 29. Bosch (Germany)               |  |

26

- IDM

Pure-play

- R&D

Rapid prototyping

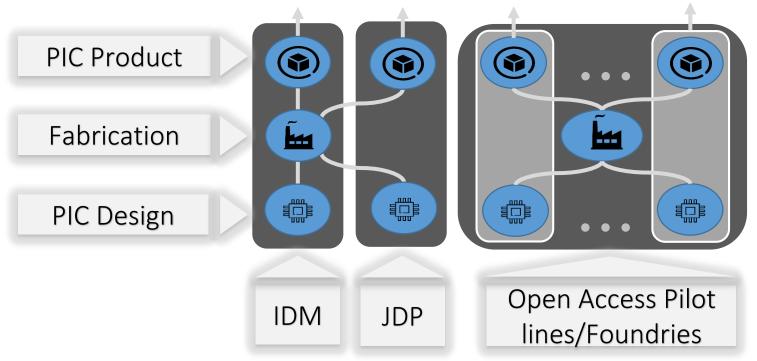

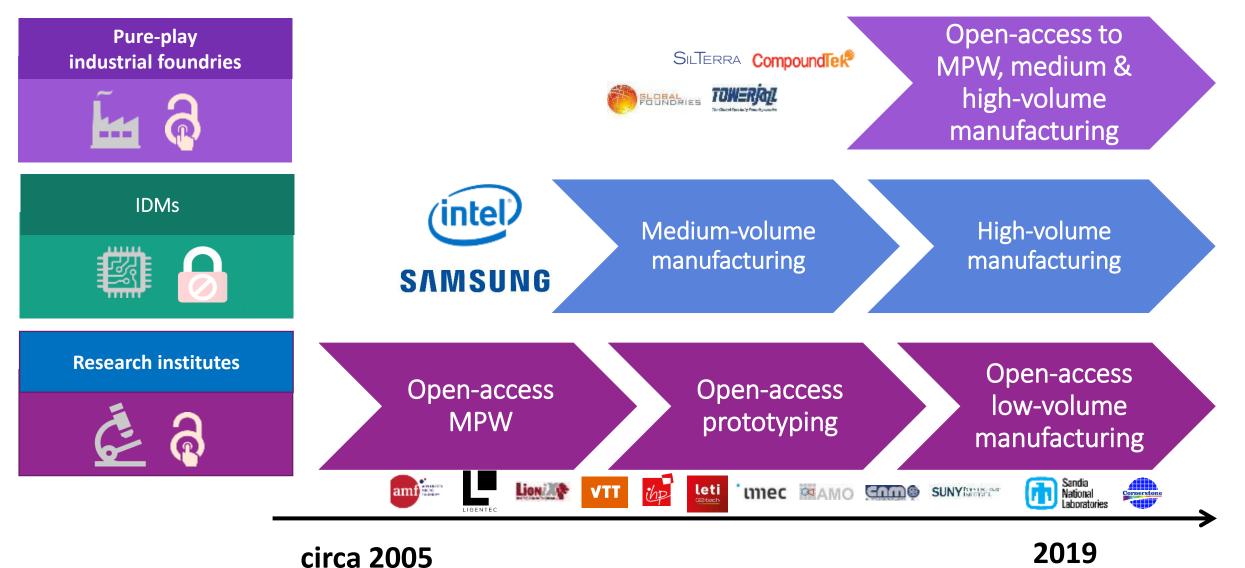

### **Access Models for Silicon Photonics ICs**

- Open access

- a model that offers fabrication services to third parties, i.e., to external users /clients outside of a technology consortium

- Generally used by fabless companies to get access to a technology

### **Open-access modes**

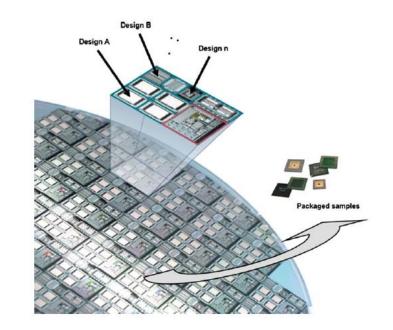

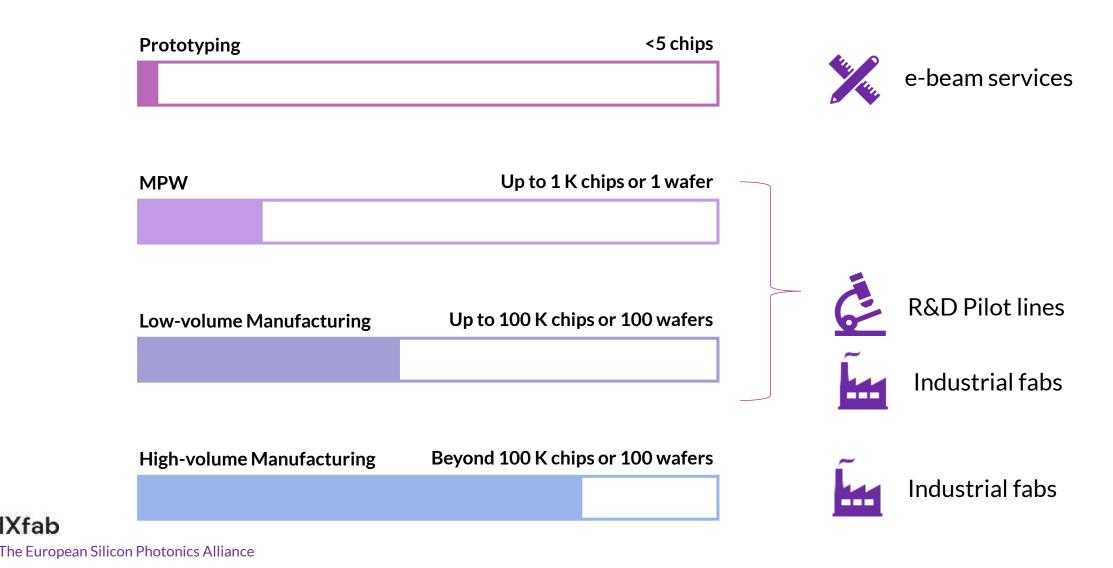

- Multi-project Wafer (MPW) runs

- For proof-of-concept and early stage R&D

- Cost sharing among various users

- Uses standardized technology

- 4 to 9 months turn-around times

- Dedicated Engineering Runs

- Avoids economic burden of optimizing custom building blocks

- Large design space to put design sweeps for optimizing

- Standardized or customized process flow

- Pre-production runs

- Volume Manufacturing

## Why is open-access important?

#### Not exhaustive

http://epixfab.eu

## **Evolution of silicon photonics prototyping & manufacturing**

• **PIXfab** The European Silicon Photonics Alliance

http://epixfab.eu

### **Economy of (wafer) scale for a standardized platform**

ePIXfab

*Volume semantics*

### Open access workflow: various ways to go

http://epixfab.eu

ePIXfab Members

http://epixfab.eu

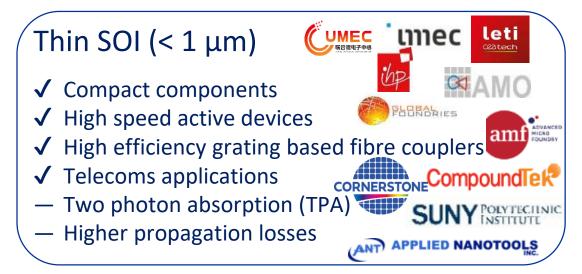

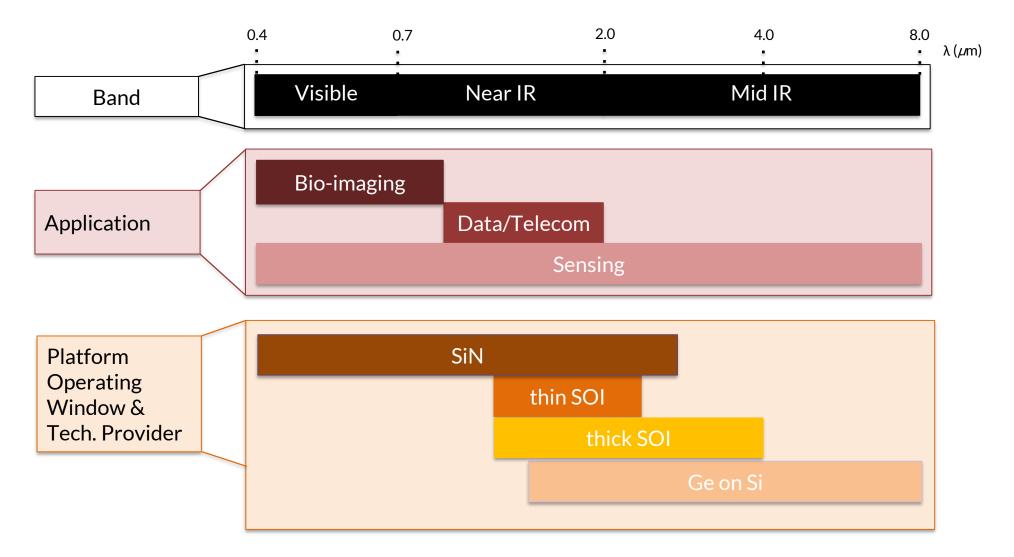

## Silicon photonics platforms

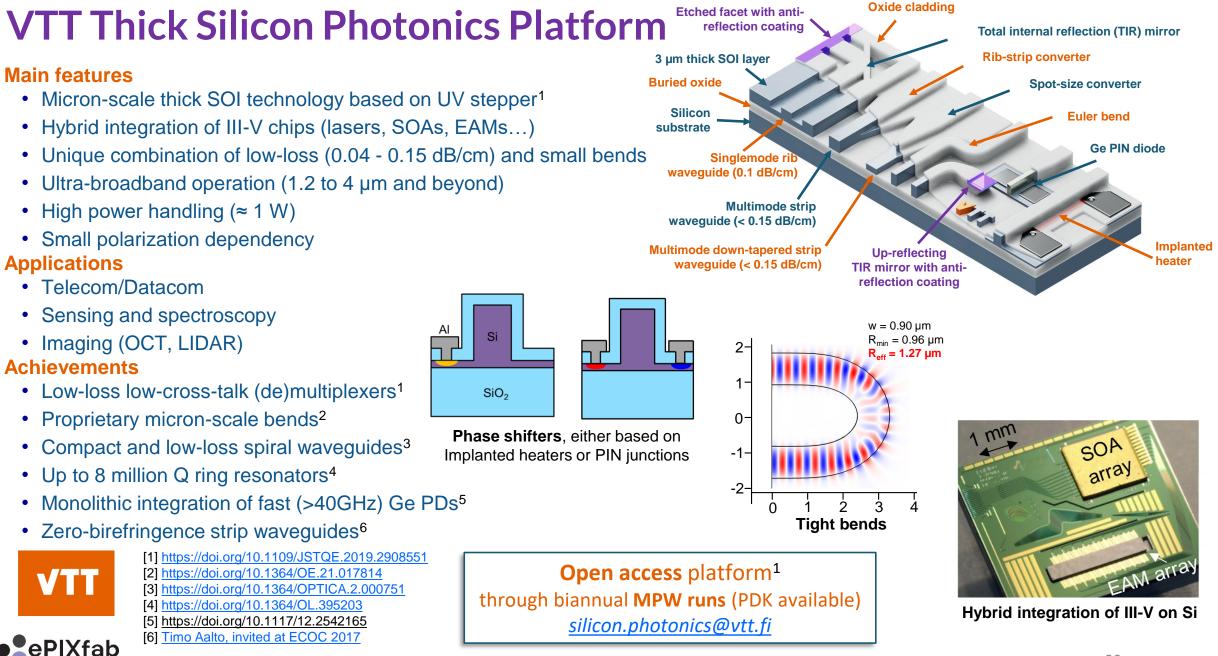

### Thick SOI (> 1 μm)

- ✓ Low-loss components

- ✓ High power applications

- ✓ Mid-IR applications

- Polarisation independence

- Low speed active components

- Large bend radius

### Silicon nitride

- ✓ Very low propagation loss

- ✓ Visible wavelength applications

- ✓ High power applications (no TPA)

- ✓ Low temperature sensitivity CORNERSTONE

- No active components

- Large component footprint SUNY POLYTECHNIC

### Ge-on-Si

ıec

- ✓ Low-loss components

- ✓ Mid-IR applications for sensing etc.

- ✓ Free-space communications

- Lower speed active components

- Larger components

VΊ

\*Example open-access foundries – not intended to be exhaustive

LIGENTEC

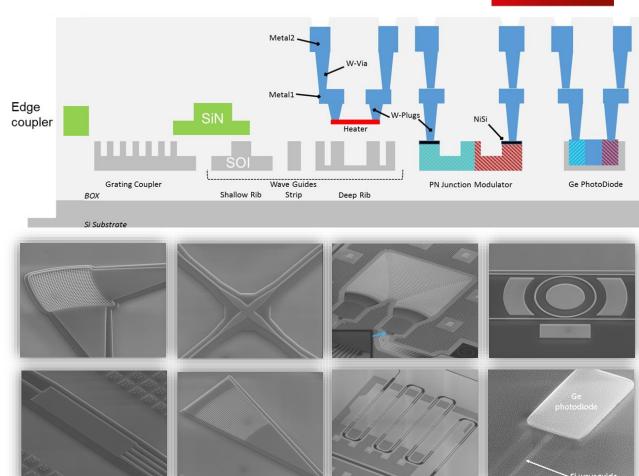

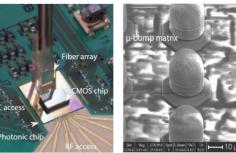

## ST Microelectronics Silicon Photonics Platform: Bilateral Mode

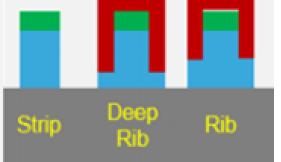

#### WG Loss

*350nm strip:* IL: 3.5 dB/cm *320nm deep-rib:* IL: 3.7 dB/cm *400nm mid-rib:* IL: 1.4 dB/cm

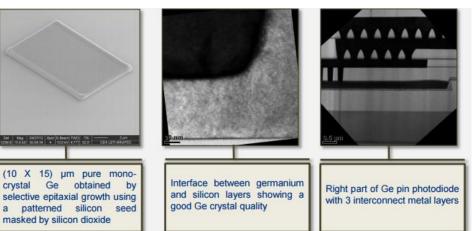

#### **Germanium Integration for High Speed Photodetector**

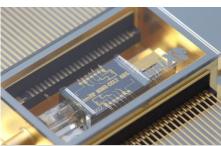

#### **System Integration: 3D integration of EIC & PIC**

Capacitor oxide

BOX

Substrate

**Capacitive Si-MOS Modulator**

PMD

Phase Shift ~ 40°/mm @ 1.8V

n-type poly-Si

Loss < 9dB/mm

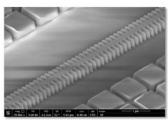

Passives: 1D & 2D Strip Photonic Crystals, 1D & 2D Rib Grating Couplers, Deep-Rib Ring Resonators ePIXfab The European Silicon Photonics Alliance

#### **Integrated Silicon Nitride**

**High-volume Manufacturing**

Beyond 100 K chips or 100 wafers

p-type SOI

p-type SOI

http://epixfab.eu

Contact

110nm ↑

# **CEA-leti's platform: Dedicated Engineering Runs**

Low-volume Manufacturing

### **Advanced 300mm Si platform**

- Design, Process integration, Test

- 220nm and 310nm SOI with 3 etch levels, metal heater and planarized BEOL with 2 routing levels

- 60nm smallest feature size

### Versatile

- Comprehensive library of mature O/C-bands components

- PECVD SiN layer option

- III-V on Si by direct bonding (wafer or dies) for lasers

- Grayscale lithography for mirror integration

### Low optical losses

- Si waveguides: 0.1-1.1 dB/cm (rib/strip)

- PECVD SiN waveguides: 0.6 dB/cm

Up to 100 K chips or 100 wafers

#### 20

....

22tech

## Imec SiN platform: Dedicated Engineering Mode

https://www.imec-int.com/en/what-we-offer/development/systemdevelopment-technologies/Integrated-photonics/silicon-nitride-basedphotonics

photonics

imager

• The European Silicon Photonics Alliance

- Extreme thickness control (<1 nm)

- Low propagation loss from 400-2200 nm

- Small bend radii (small footprint)

- High power handling

- Processing on Si & quartz wafer

- Low coupling loss (GC and EC)

- Integration with SiP advance actives (modulator, GePD)

- Wafer bonding capability (e.g. CMOS wafer to photonic wafer)

Low-volume Manufacturing

Advance laser

Lidar

#### Up to 100 K chips or 100 wafers

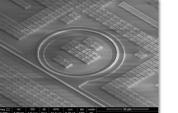

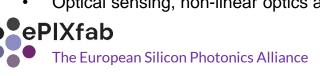

#### **Standardized Open Access SOI Technologies via MPW through brokers** Accessible through MPW and dedicated engineering runs umec leti EUROPRACT latech IC SERVICE **Passive + heaters IHP SG25\_PIC** PSV+ Metal routing & Pad Si **ISIPP50G** Ge 0 strip strip strip bated bates bates AlCu Si fiber coupler with Lightpose SI-WG Si310-PH IHP SG25H4\_EPIC TM1 Ge PIN PE AlCu SiO 310, 220 nm SOI platform 220 nm SOI platform Photonic BiCMOS *O band devices compatible* O and C band Monolithic integration C-band for III-V laser integration 50G active devices & BiCMOS (190GHz HBT)

Low-volume Manufacturing

Up to 100 K chips or 100 wafers

### Standardized Open Access SOI Technologies via MPW (Direct Access)

Accessible through MPW and dedicated engineering runs

### **Standardized Open Access SOI Technologies: Rapid Prototyping**

Rapid Prototyping and Customized Prototyping Services

#### Prototyping/MPW

Up to 1 K chips or 1 wafer

### Technology Updates 2021

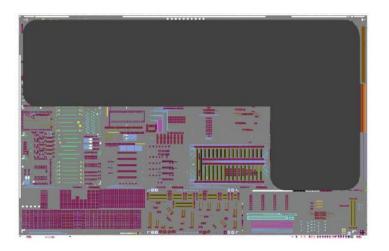

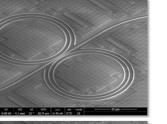

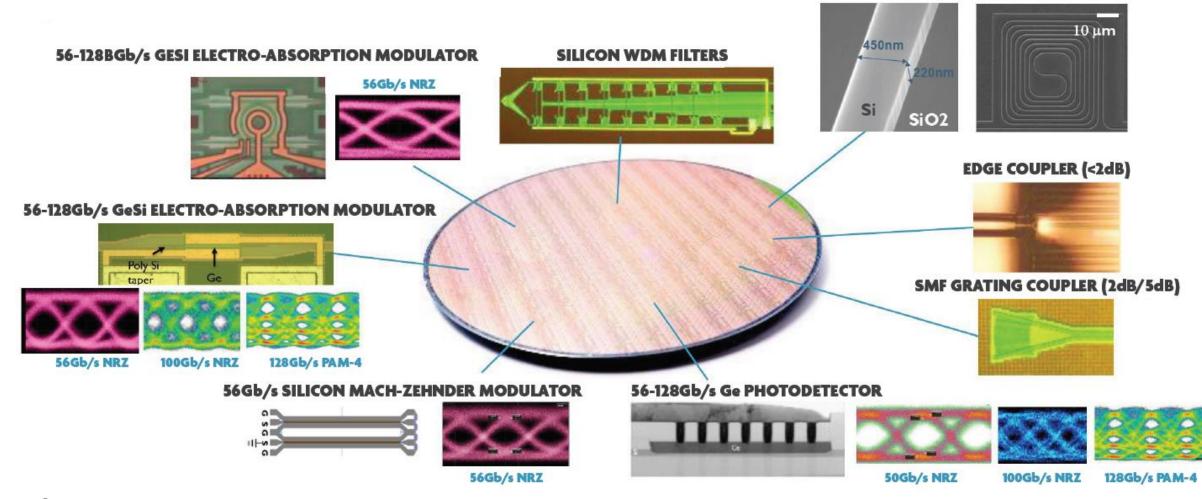

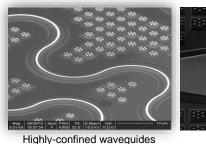

### imec's iSiPP50G platform

#### LOW-LOSS HIGH-DENSITY PASSIVE WAVEGUIDE CIRCUITS

### **CEA-LETI Si-310 technology**

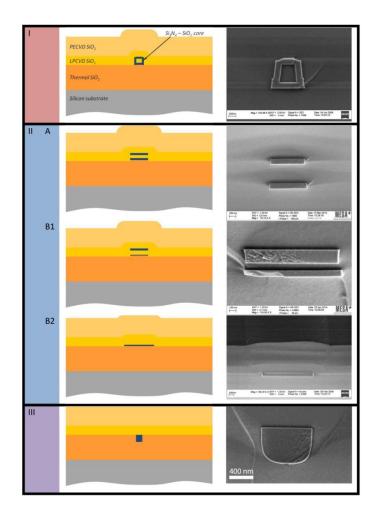

#### Process characteristics $\rightarrow$ state-of-the art technology

- 310nm SOI & 2µm BOX on 300mm wafers

- Ge deposition for photodiodes and SiN module option

- 193nm immersion lithography enabling feature size down to 100nm

- 3 Si patterning steps for waveguides & 6 implant operations for modulators

- 2 metal layers for optimal routing & bump deposition for flip-chip

Cross-sectional schematic

### Library contents & indicative performances $\rightarrow$ high performance building blocks for 1310 & 1550nm

| Active components              | Specifications     | Value @ 1550nm |

|--------------------------------|--------------------|----------------|

| Mach-Zehnder modulator         | OE bandwidth @ -4V | 40GHz          |

|                                | Vpi.Lpi @ -2V      | < 2V.cm        |

| Ring racetrack modulator       | OE bandwidth @ -2V | > 15GHz        |

|                                | Vpi.Lpi @ -2V      | < 2.5V.cm      |

| Longitudinal PiN Ge photodiode | EO bandwidth @ -1V | > 35 GHz       |

|                                | Dark Current @-1V  | < 55nA         |

| Passive components               | Specifications | Value @ 1550nm |

|----------------------------------|----------------|----------------|

| Strip, rib & deep rib waveguides | Loss           | < 1dB/cm       |

| Transitions                      | Loss           | < 0.03dB       |

| 1D grating coupler               | Insertion loss | < 2.5dB        |

| 2D grating coupler               | Insertion loss | < 3.5dB        |

| Ring filter                      | Quality factor | > 10,000       |

| MultiMode interferometer 1x2     | Loss           | < 0.2 dB       |

Mach-Zehnder modulator

### Applications $\rightarrow$ well-adapted to R&D

- Comunication: telecom/datacom, 5G infrastructures

- Computing: quantum & neuromorphic computing

- Optical sensing: gas sensing, health monitoring...

ePIXfab

The European Silicon Photonics Alliance

#### MPW offer

- 1 run offered per year

- Price based on circuit area

- PDK available with Cadence, Tanner & Synopsys tools

3D system integration

Bump deposition

leti

Ceatech

ANDELEC

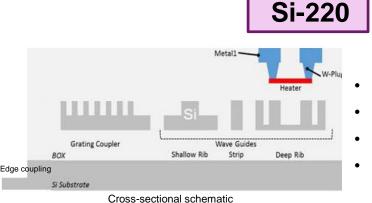

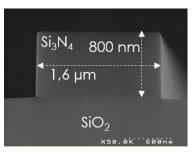

## **CEA-LETI Si-220 & Si<sub>3</sub>N<sub>4</sub>-800 technologies**

#### **Process characteristics**

800nm LPCVD Si3N4

200mm wafers

200nm CDmin

- 220nm SOI & 2µm BOX

- 300mm wafers

- 193nm immersion lithography

- Passive components only

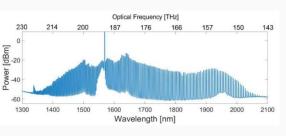

### Si<sub>3</sub>N<sub>4</sub>-800

### Library contents & indicative performances

1D grating coupler

Heaters

+ transitions (singlemode to multimode), directional couplers, multimode interferometers... Performances close to those obtained with Si-310 technology

### **Applications**

- Comunication, computing & optical sensing for Si-220

- Optical sensing, non-linear optics and quantum photonics for  $Si_3N_4$

٠

| Components                   | Specifications          | Value @ 1550nm     |

|------------------------------|-------------------------|--------------------|

| Straight & bend waveguides   | Loss                    | Down to 0.03 dB/cm |

| 1D grating coupler           | Insertion loss          | < 12.5 dB          |

| MultiMode Interferometer 1x2 | Insertion loss          | < 0.1 dB           |

| MultiMode Interferometer 2x2 | Insertion loss          | < 0.5 dB           |

| Racetrack resonators         | Attenuation coefficient | 3 dB/m             |

|                              | Quality factor          | 10 <sup>7</sup>    |

### MPW offer

- 1 run offered per year for Si-220/1 or 2 for Si<sub>3</sub>N<sub>4</sub> ٠

- Price based on circuit area

- PDK available with Cadence tool

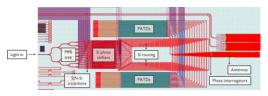

## **IHP's photonic-electronic platform**

The European Silicon Photonics Alliance

ePIXfab

http://epixfab.eu

The European Silicon Photonics Alliance

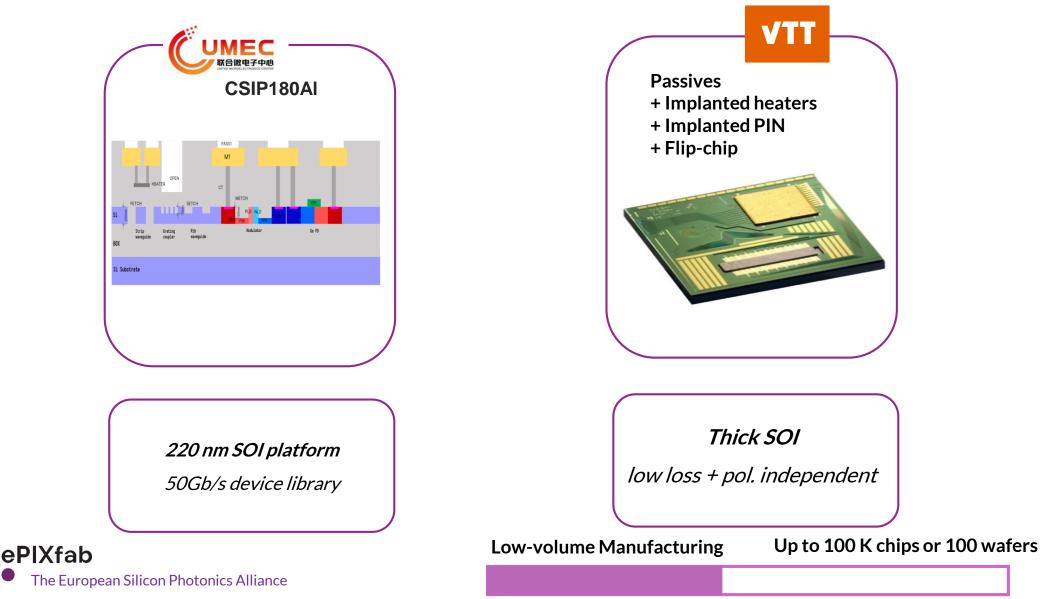

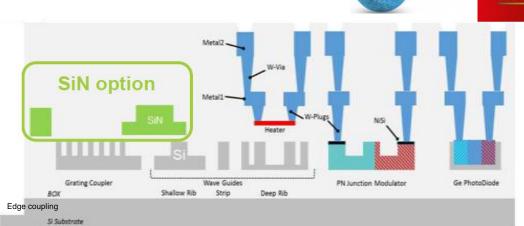

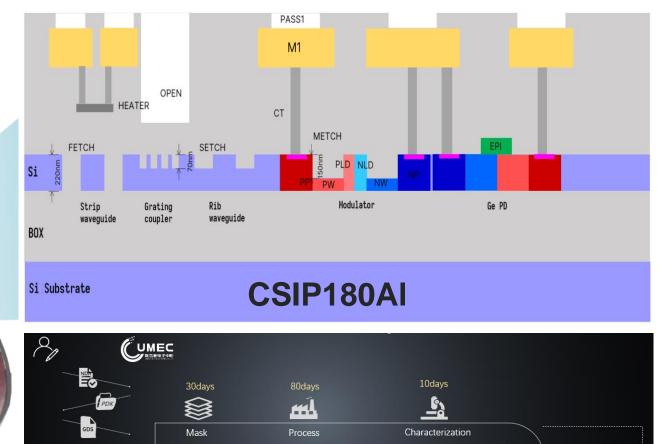

### **Silicon Photonics Platform**

Ref: https://service.cumec.cn/

- 180nm technology node (130nm in 2021)

- Passive & Active devices

- >50Gbps device library...

120 days

÷

Packaging

€JJ

Delivery

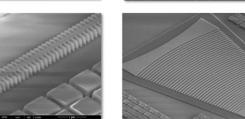

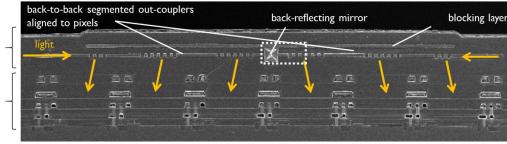

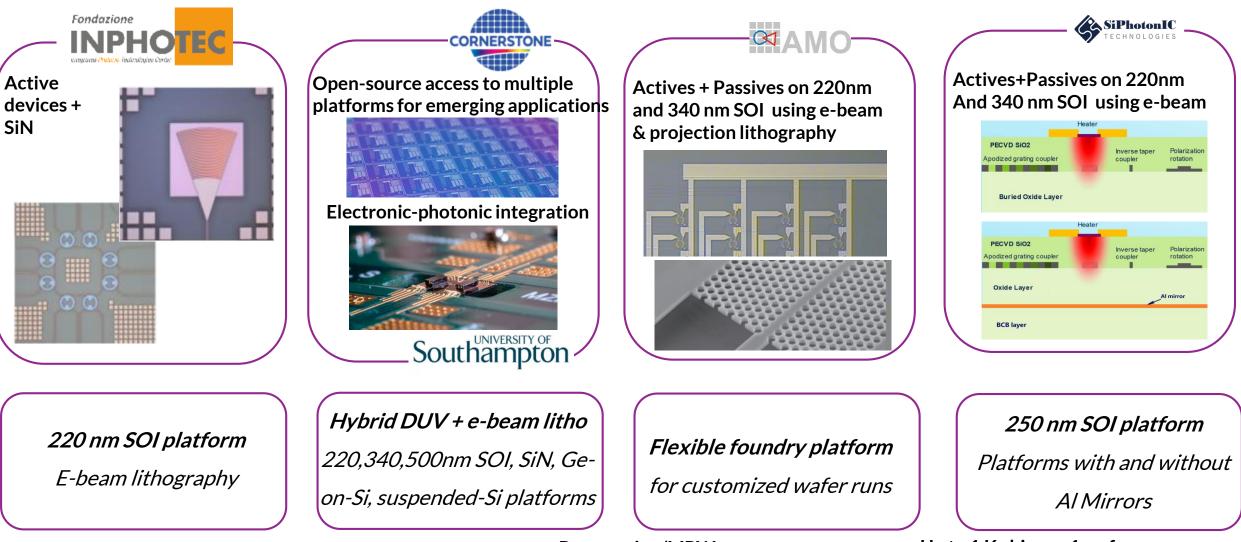

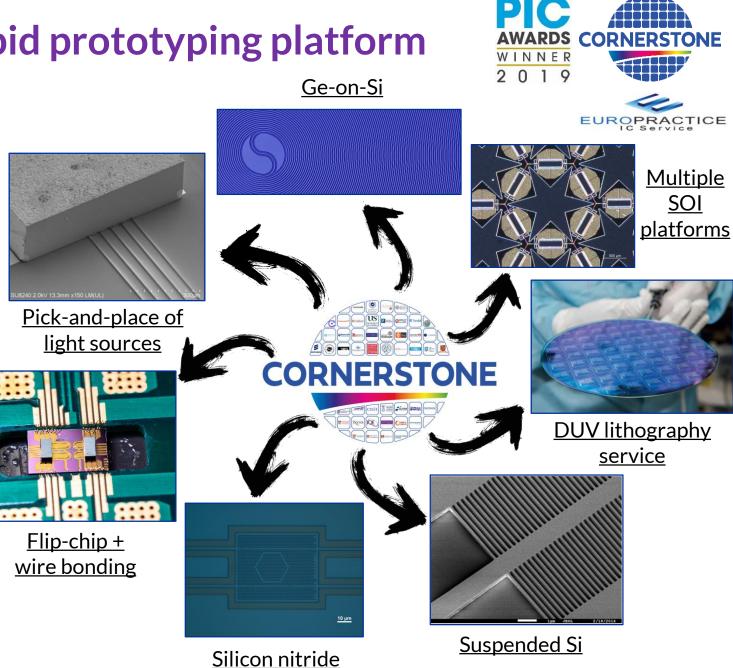

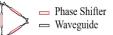

# **CORNERSTONE's flexible rapid prototyping platform**

- License free, open-source platforms

- Hybrid DUV + e-beam lithography to enable seamless scaling to higher volumes

- Multiple platforms for visible, telecom and mid-IR wavelengths

- Versatile fabrication processes via MPW service & bespoke batches

- Design consultancy available

Core values:

- To give process flexibility back to the designer

- To enable rapid prototyping using scalable technology

### SiPhotonIC's platform

- State-of-the-art 100kV E-Beam Writer JBX-9500FSZ

- Advanced SOI platform

- Al mirror introduced with grating coupler for ultra-low loss fiber-to-chip coupling

- > Efficient Ti metal heater

- > Full building blocks to build your silicon PICs

- Large scale silicon PIC prototyping

- Ultra-small structure resolving

- > Fast turn over period

| Typical components            | Performances                                        |

|-------------------------------|-----------------------------------------------------|

| Grating coupler               | coupling loss: <1.0 dB                              |

| Strip waveguide               | Propagation loss:<br><2.5dB/cm                      |

| Mach–Zehnder switch           | Insertion loss: <0.1dB                              |

| Cross intersection            | Insertion<br>loss:~0.1dB/cross<br>Crosstalk: <-40dB |

| Thermal tunable phase shifter | Tunability: > 2π                                    |

• Selected publications

• Large-scale silicon quantum chip for high-dimensional quantum entanglement generation and manipulation.

Silicon quantum photonic chip for quantum teleportation and multiphoton entanglement.

• Silicon quantum photonic chip for generation and sampling of quantum states on chip.

#### SCIENTIFIC REPORTS

• Silicon chip for multicore fiber switching.

The European Shicon Photonics Aniance

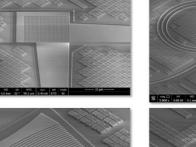

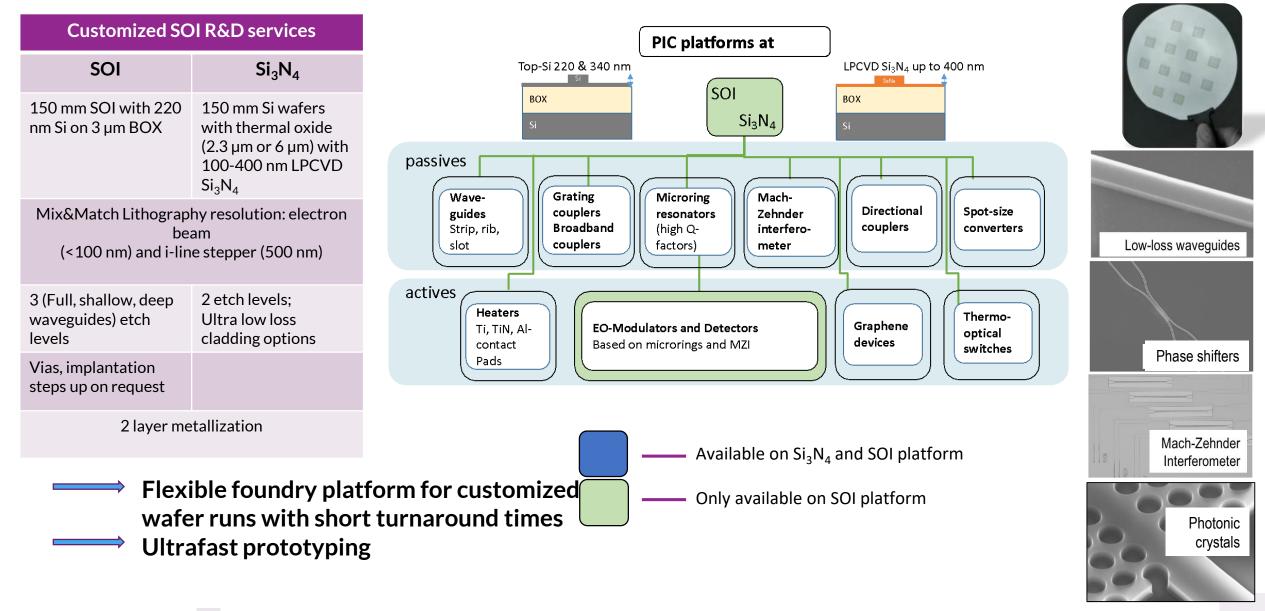

### AMO's eBeam-based prototyping of SOI and silicon nitride PICs

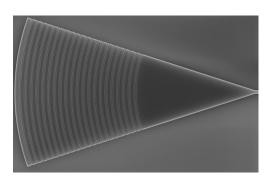

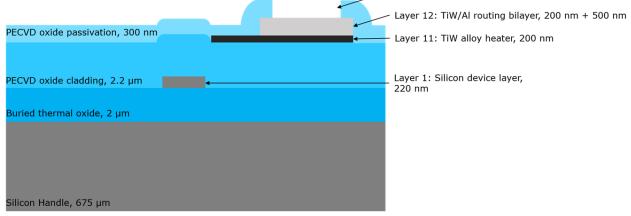

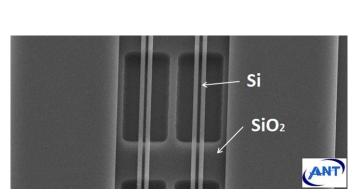

## **Applied Nanotools e-beam prototyping platform**

- Various platforms available: 220 nm, 300 nm, 500 nm SOI and 400 nm SiN

- 70 nm minimum feature size (suitable for sub-wavelength devices)

- Fast turnaround time and competitive pricing

- Efficient TiW metal heaters for >2π phase shifting

- Low-loss waveguides with < 2 dB/cm propagation loss

- Vertical grating couplers and edge couplers available in our PDK

- Online resources, submission system and design rule checks via. Design Center: <u>https://www.appliednt.com/nanosoi/sys/</u>

- 8 multi-project wafer (MPW) runs provided annually; dedicated runs available by request

- Custom fabrication options: multi-layer etching, custom metal, oxide window openings, suspended waveguide devices, etc.

Vertical grating coupler

The European Silicon Photonics Alliance

PIXfab

Microring resonator

**NANOSOI**

Integrated Photonics Fab

Suspended slot waveguides

Layer 13: Oxide window

### **Expanding silicon photonics portfolio**

## Limitations of current silicon-on-insulator PICs\*

| Spectral transparency: shortest $\lambda$  | 1.1 µm       | Silicon bandgap                      |

|--------------------------------------------|--------------|--------------------------------------|

| Spectral transparency: longest $\lambda$   | 4 µm         | SiO2 absorption                      |

| Optical power limitation (1.3/1.5 $\mu$ m) | 10's of mW   | Two-photon absorption                |

| Distributed backscatter                    | %'s per cm   | nm-level sidewall roughness + HIC    |

| Optical pathlength error                   | 0.1% - level | nm-level width inaccuracy + HIC      |

| T-sensitivity of pathlength                | 0.01%/K      | Thermo-optic coeff. silicon          |

| Layer stack flexibility                    | Limited      | SOI-wafers made by bonding           |

| Integration with CMOS electronics          | Challenging  | Technical or economic mismatch       |

| Source integration                         | Challenging  | Technology not available in CMOS-fab |

#### **Silicon Photonics beyond Silicon**

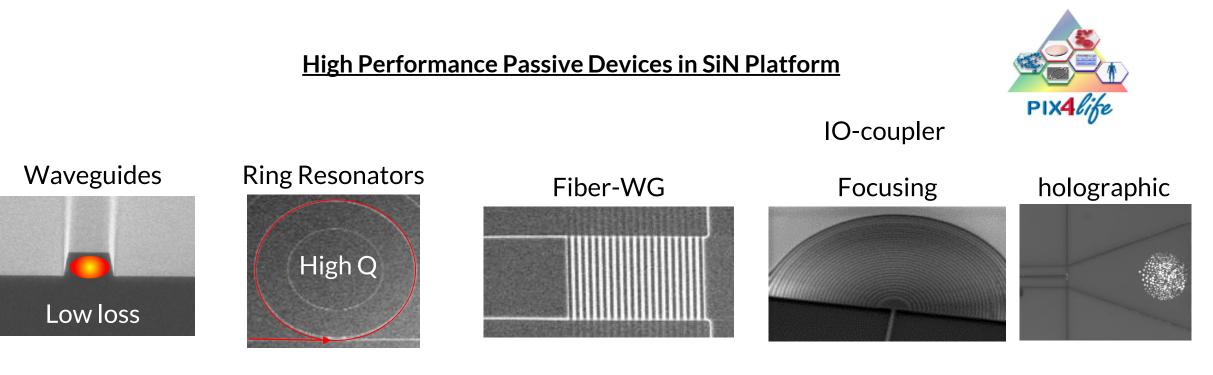

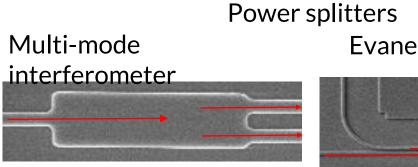

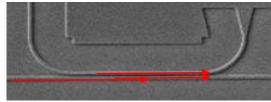

## **Open Access Silicon Nitride Technologies**

Accessible through MPW (via brokers or directly) and dedicated engineering runs

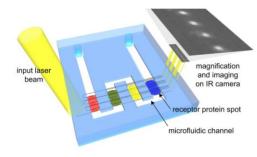

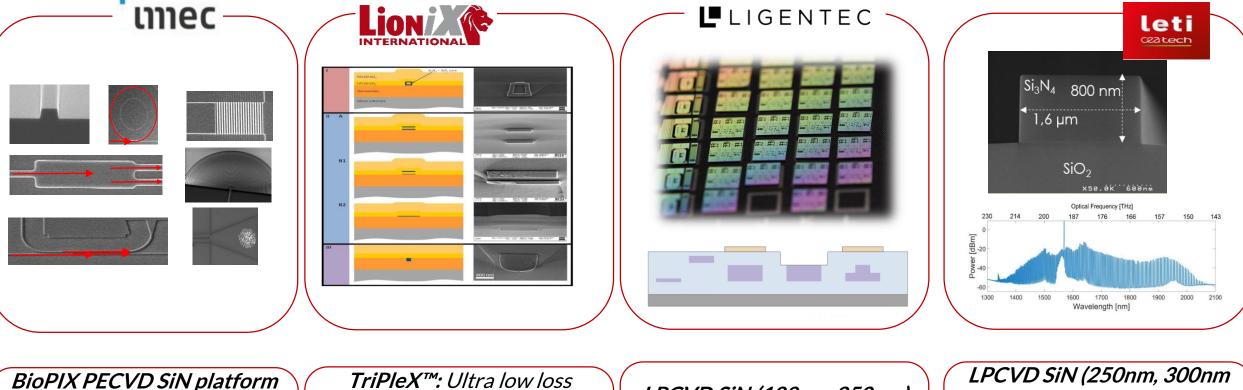

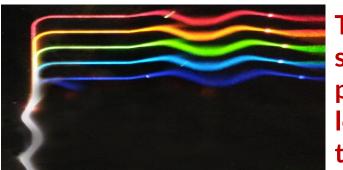

High performance platform for life-science applications at visible wavelength ranges *TriPleX™: Ultra low loss building blocks for telecom, bio photonics and bio sensing applications*

LPCVD SiN (100nm-850nm) SiN core for low loss visible, telecom and MidIR *LPCVD SiN (250nm, 300nm and 800nm thick) Biosensors, Quantum photonics, Non-linear optics*

Low-volume Manufacturing

Up to 100 K chips or 100 wafers

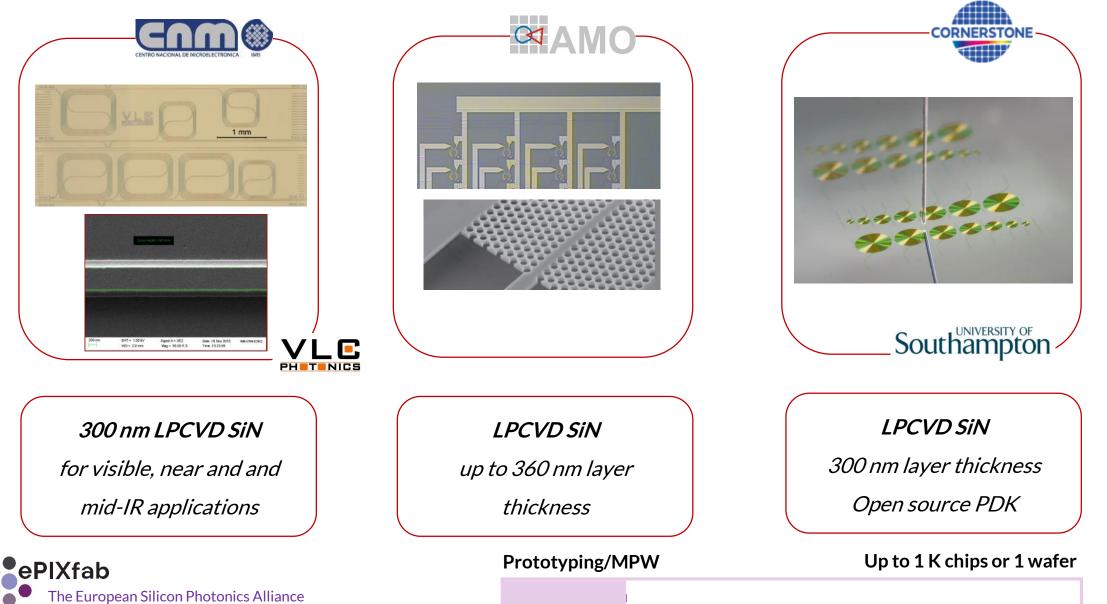

### **Open Access Silicon Nitride Technologies**

Rapid Prototyping and Customized Prototyping Services

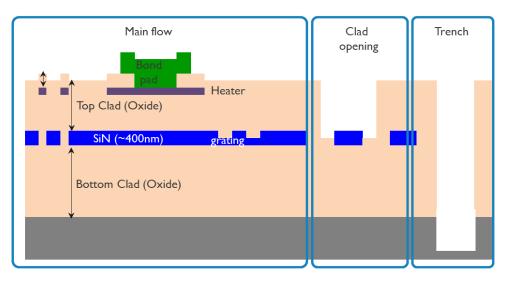

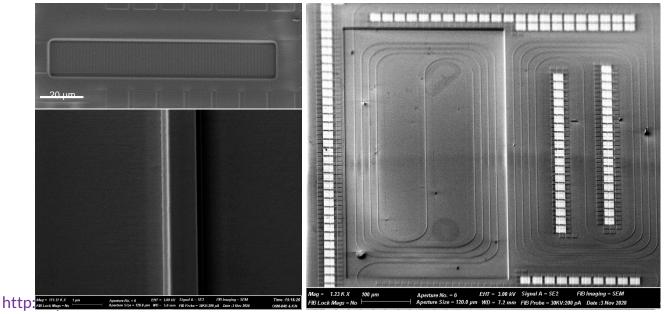

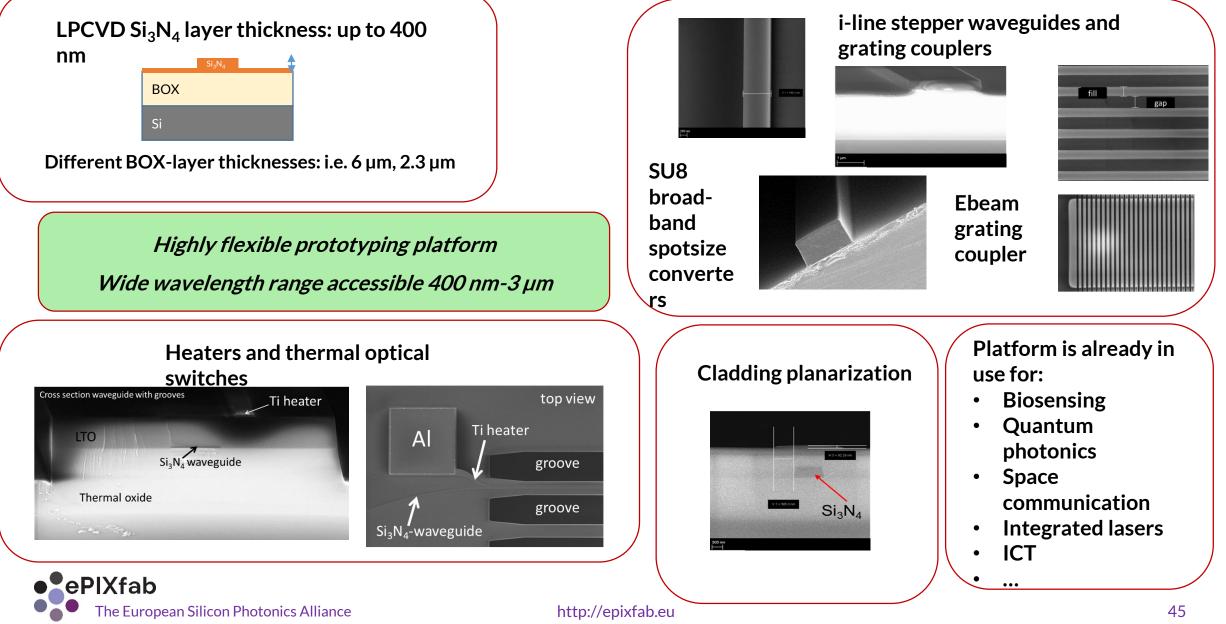

# **LPCVD SiN Platform**

### High quality LPCVD Si<sub>3</sub>N<sub>4</sub>

- Design, Process integration, Test

- Stoechiometric SiN

- 200mm wafers with subtractive process

- Cladding opening

- 250nm, 300nm and 800nm thick, other thicknesses on demand with thermal oxide for better thickness control

### **Record low optical losses**

Ultra-Low loss thanks to smoothing annealing: 0.03dB/cm for tighly confined strip waveguide in S/C/L-bands

### **ULLSIN PDK**

800nm LPCVD SiN PDK including: grating & directional couplers, 1x2 & 2x2 MMI, Y-junction, 10µm bending radius, s-bend, racetrack resonator with Q-factor >5×10<sup>6</sup>

#### APPLICATION from UV to MIR Biosensors

- LIDAR

- Quantum photonics

Non-linear optics, comb generation

#### PUBLICATIONS

- S. Boust et al, Microcomb Source Based on InP DFB / Si<sub>3</sub>N<sub>4</sub> Microring Butt-Coupling, Journal of Lightwave Technology 2020

- H. El Dirani et al, Ultralow-loss tightly confining  $Si_3N_4$  waveguides and high-Q microresonators, Optics Express 2019

# LIGENTEC LPCVD all-nitride core platform

# LIGENTEC

### Full Creativity (PDK)

- ✓ Couplers

- Mux / DeMux

- ✓ MZIs / DLIs

- Resonators

- Polarization control

#### Actives

**The Basics**

- Electrical Tuning

Modulators (hybrid)

- ✓ Lasers (hybrid)

- ✓ Detectors (hybrid)

### **World Connections**

- Edge / Grating Coupler

- Spot Size Converter

- Arbitrary Die Shape

- Bond pads

- Cladding opening for sensing

High Mode Confinement

Small Footprint (50µm bend)

Low Loss (< 0.1dB/cm)

High Power (>10W)

8 MPW/year

**Dedicated runs**

10 weeks turn around

Flexible R&D line

Volume line

### **TriPleX<sup>TM</sup> platform**

The flexible silicon nitride platform: low loss, wide transparency

- Low optical attenuation from 405-2350 nm

- Adjustable polarization properties (sensors, telecom)

- Small bend radii (small footprint!)

- Flexible properties geometry by design

- Silicon and glass **compatible**

- Spot size converters for

- low loss fiber chip coupling

- hybrid integration

Telecom/datacom

Life Science

Metrology

### **BioPIX PECVD SiN platform**

່ເກາec

plitters Evanescent coupler

http://epixfab.eu

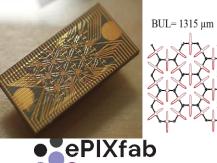

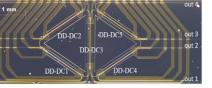

## **CNM SiN photonic platform**

The process technical features, are:

Wavelength range from Visible to Mid infrared

Three waveguide cross-sections (nitride films 300/340 nm height, shallow 150/300 nm, deep 300 and mini-deep 150 nm)

- Thermo-optic tuners (Cr/Au, Poly-Si, AI-5% Cu...High flexibility)

- Selective area trenching: integration Biosensors+PICs

Spot size converters for low loss fiber chip coupling (under development)

10 Hexagonal Cells size: 5.5 x 11 mm

The European Silicon Photonics Alliance

## AMO's LPCVD silicon nitride PICs

# **EUROPRACTICE + CMP : MPW in 6 Silicon Photonics foundries**

### **Technology Access: IP and licensing**

- Most foundries require a license agreement to be signed to access the PDK

- Typical IP assignment:

- Foundry owns manufacturing IP and know-how

- Foundry may own IP protected black-box components/designs

- Designer may own new device design IP

- IP is maintained by ensuring that other users on an MPW run do not see your designs

- An NDA is often signed with all parties

- Foundries often have a model in place for IP licensing

- Technology transfer between foundries (i.e. for ramp-up in volume) can be challenging

### **Current status of open-access foundry services**

| Attribute                                               | Status                                         |

|---------------------------------------------------------|------------------------------------------------|

| Application spectrum of silicon photonics PIC platforms | Visible to mid-IR, myriad applications         |

| Maturity of Silicon Photonics Platforms                 | High                                           |

| MPW turnaround time                                     | 3 to 6 months                                  |

| Prospects for scaling up volumes by European fabs       | Low to medium volume<br>manufacturing possible |

| Prospects for high-volume manufacturing in Europe       | Currently only in partnership with non-EU fabs |

| Brokerage services for Silicon Photonics MPW            | Possible                                       |

| Design support                                          | Possible                                       |

| Training, education and skill development               | Possible                                       |

### You need more than just a fab

• Design and simulation tools: the market is evolving

• Packaging: strong progress is past several years

Abdul Rahim, Ph.D Coordinator

**Prof. Roel Baets** Chairperson

William Chen, Ph.D **China Liaison Officer**

http://epixfab.eu

info@ePIXfab.eu +32 9 331 4843 []]] /groups/4888115